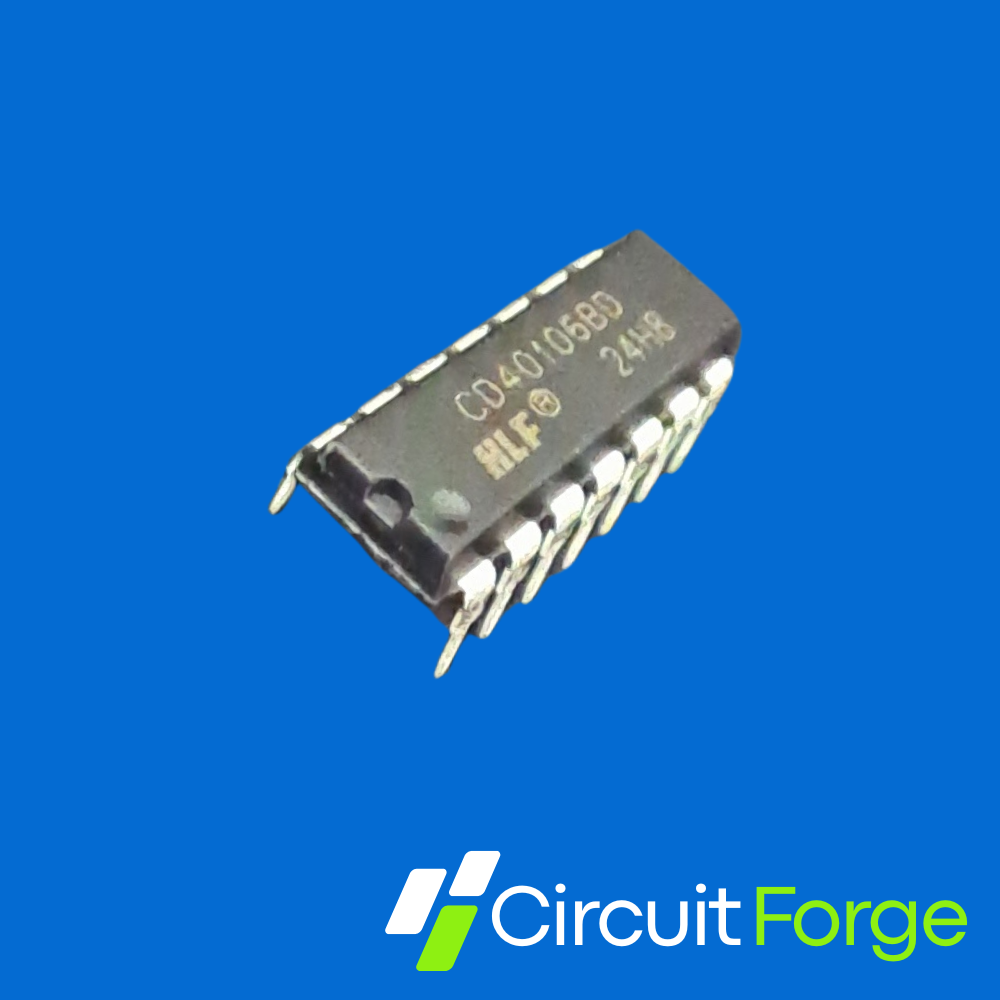

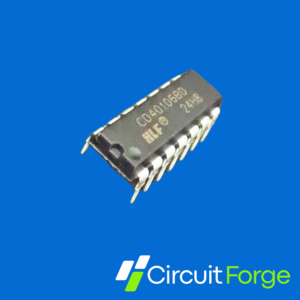

CD40106 — Hex Schmitt Trigger Inverter | DIP14

Overview

The CD40106 is a low-power CMOS Hex Schmitt Trigger Inverter featuring six independent

Schmitt-trigger circuits designed for superior noise immunity, stable switching, and clean digital edge shaping.

With its wide operating voltage of 3V to 18V and ultra-low input current, it is ideal for waveform shaping,

oscillators, debounce circuits, and digital conditioning in noisy environments.

🔧 Ideal for: oscillators, debouncers, digital conditioning, wave shaping & mixed-signal circuits.

Why CD40106?

The CD40106 integrates six Schmitt trigger inverters, each offering hysteresis and noise filtering capability.

Its CMOS architecture ensures extremely low static power consumption, while the wide supply range makes it suitable

for both low-voltage logic systems and higher-voltage industrial circuits.

This device excels in waveform cleanup, debounce applications, and oscillator design thanks to its consistent

switching thresholds and low input leakage.

Key Advantages

- 🔰 Schmitt Trigger Inputs — Excellent noise immunity and clean transitions.

- 🪫 Ultra-Low Leakage — Input currents as low as 0.01 µA.

- 🔋 Wide Voltage Flexibility — Operates from 3V to 18V.

- 🔁 Six Independent Channels — Ideal for multi-signal conditioning.

- ⚙️ Fast Switching — ns-level delays suitable for high-speed logic applications.

Technical Specifications

| Parameter | Value / Range | Notes |

|---|---|---|

| Operating Voltage | 3V – 18V | Wide-range CMOS operation |

| Input Current | ≤ 1 µA | As per datasheet |

| Hysteresis Voltage | 1.3V @ 5V, up to 3.2V @ 15V | Stable switching behaviour |

| Output Drive Current | Up to ±22 mA | Depends on VDD |

| Propagation Delay | 35–80 ns (VDD dependent) | From AC characteristics |

| Package Options | DIP14 | DIP: 1000/box |

Applications

⏱️ Oscillators & Timers

Use in RC oscillators for frequency generation.

🔔 Switch Debouncing

Clean noisy mechanical switch inputs.

📟 Signal Conditioning

Wave shaping and edge cleaning in digital chains.

🔄 Level Translation

Useful in mixed-voltage digital systems.

Design Tips

- Add a small input capacitor (10–100 pF) to tame noisy edges.

- Place a decoupling capacitor close to VDD–VSS pins.

- Use short traces to avoid unwanted ringing.

- Leverage hysteresis for cleaning slow or analog transitions.